|

|

|

Dupa cum s-a vazut, pe placa de baza a calculatorului PC exista un circuit de ceas (clock) care genereaza un semnal de o anumita frecventa - 14,3 Mhz la PC original si peste 3 GHz la calculatoarele actuale -, folosit pentru executia sincronizata a operatiilor din interiorul micriprocesorului si efectuarea transferurilor intre diferite blocuri la nivelul magistralei externe.

In timpul functionarii, activitatea microprocesorului poate fi descompusa in secvente de microoperatii, care formeaza asa-numitii cicli masina. In functie de natura operatiei care se executa, putem avea 5 tipuri de cicli masina:

1. Citire (read) atunci cand se citesc date din memorie sau de la dispozitivele de I/O

2. Scriere (write) - cand datele se inscriu in locatii de memorie sau intr-un dispozitiv de I/O

3. Recunoastere intrerupere - in cazul generarii unei cereri de intrerupere pe care mP o identifica

Oprire (halt) - atunci cand microprocesorul este oprit pana la primirea unei cereri de intrerupere

5. Arbitrare magistrala - cand sistemul de calcul este prevazut cu mai multe microprocesoare care pot avea acces la o magistrala comuna

Toate aceste operatii sunt descrise cu lux de amanunte in foile de catalog ale firmelor ce produc microprocesoare. Fara a le detalia aici, aratam doar care este semnificatia unei diagrame de semnal.

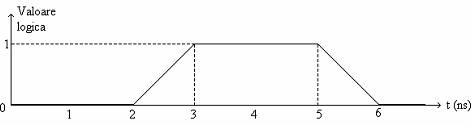

Fig. 1.

Dupa cum se observa in figura 1, semnalul reprezentat are valoarea '0' logic la t=0, la t=2 incepe sa creasca spre 1 logic, la t=3 deja este '1' logic, se mentine 2 ns si apoi 'cade' inapoi la '0' logic. Acest mod de reprezentare a semnalelor se numeste diagrama de semnal. In figura 1 este prezentata diagrama semnalului de ceas (clock).

In practica exista un mare numar de semnale care intervin in desfasurarea ciclilor masina. Pentru fiecare tip de ciclu exista cate o diagrama de semnal, iar distributia in timp a semnalelor este specifica fiecarui tip de ciclu.

Programul care se executa se gaseste memorat in segmentul de cod. Dupa cum am vazut intr-un capitol anterior, cand se incarca o instructiune din memorie adresa acestuia este furnizata de registrii CS (ca adresa de baza) si respectiv IP sau EIP (ca deplasament). In mod normal, continutul registrului (E)IP este incrementat pe masura ce instructiunile se executa, astfel ca totdeauna sa fie deja selectata instructiunea care urmeaza. Instructiunile de salt neconditionat sau apel de procedura pot insa modifica valorile registrilor (E)IP si eventual CS, modificandu-se astfel ordinea secventiala de executie a instructiunilor.

Datele din memorie care formeaza operanzii instructiunilor pot fi adresate in mai multe moduri. Acesti operanzi pot fi continuti in registri, in memorie, in instructiuni sau porturi de I/O. Operatiile care implica date numai din registri sunt cele mai rapide, nefiind nevoie de utilizarea magistralei pentru acces la memorie.

Registrii folositi si modul de adresare (memorie sau registru) sunt codificati in interiorul instructiunii. In practica exista urmatoarele tipuri de adresare:

1. Adresare imediata

In acest caz operandul apare chiar in instructiune.

mov ax,5

mov eax,5

Aceasta instructiune va initializa registrul (E)AX cu valoarea 5. Evident, a doua instructiune poate fi folosita numai la microprocesoarele pe 32 biti, care contin registrul EAX.

2. Adresare directa

Deplasament in interiorul segmentului curent (de obicei in interiorul segmentului de date) este furnizat de catre instructiune.

add bx,[200]

Aceasta instructiune aduna la registrul (E)BX continutul locatiei de la adresa efectiva 200 din segmentul de date.

3. Adresare indirecta (prin registri)

La procesoarele pe 16 biti, offsetul este furnizat de unul dintre registrii BX, SI sau DI, iar registrul implicit este bineinteles DS. In cazul procesoarelor pe 32 biti, pentru offset poate fi folosit oricare registru general pe 32 biti.

mov al,[bx]

mov al,[ebx]

Continutul adresei de memorie de la adresa data de (E)BX este transferat in AL. Observam ca procesoarele pe 32 biti pot lucra si cu registri de 16 sau 8 biti pentru date, dar nu si pentru adrese (care au intotdeauna 32 biti).

Adresare bazata sau indexata

Offsetul se obtine adunand la unul din registrii de baza (BX sau BP) sau index (SI sau DI) un deplasament constant. Din nou, la procesoarele pe 32 biti se poate folosi suma a oricare 2 registri generali.

mov ax,[bx+5]

mov ax,[ebx+5]

La continutul adresei din (E)BX se aduna deplasamentul 5 si se obtine offsetul operandului. Aceste tipuri de adresare se pot folosi cand avem structuri de date de tip tablou, care pot fi localizate in diferite locuri din memorie. Constanta va contine offsetul la care incepe structura de date, iar deplasamentul va furniza pozitia elementelor in cadrul structurii.

5. Adresare bazata si indexata

Este cea mai complexa forma de adresare, care combina variantele anterioare, permitand adresarea cu 2 indecsi (continuturile registrilor de baza si indecsi la procesoarele pe 16 biti, oricare 2 registri generali la procesoarele pe 32 biti).

mov ax,[bx+si+7]

mov eax,[ebx+ecx+9]

Procesoarele pe 32 biti permit si o forma extinsa a ultimelor doua tipuri de adresare. Mai exact, registrul folosit pentru offset (pentru adresarea bazata sau indexata), respectiv unul din cei 2 registri (pentru adresarea bazata si indexata), poate fi inmultit cu 2, 4, sau 8. In acest mod pot fi accesate mai usor tablourile cu elemente avand dimensiunea de 2, 4, sau 8 octeti (cum sunt tipurile standard).

mov ax,[ebx*4+5]

mov eax,[ebx+ecx*2+9]

In cele aratate anterior, de obicei registrul segment implicit este cel de date, presupunand ca se adreseaza operanzi de calcul obisnuiti. Exceptia este data de cazul cand se foloseste BP, atunci registrul de segment implicit fiind SS. Daca se doreste folosirea altui registru de segment decat cel implicit, in instructiune se va preciza explicit despre care registru de segment este vorba, cum ar fi in instructiunea urmatoare:

mov bx,es: bp+7

Daca nu precizam ES, implicit se folosea SS, deoarece registrul de baza este BP.

O zona speciala de memorie este folosita de programe atunci cand se executa subprograme sau se transmit parametrii de la un program la altul.

Aceasta zona poarta numele de stiva (in engleza stack), fiindca functionarea ei este asemanatoare cu cea a unei stive fizice de obiecte. Modul de funtionare al stivei este numit LIFO (Last Input - First Output). Intr-o stiva, datele au voie sa fie depuse numai prin partea superioara, astfel incat informatia depus ultima data (Last Input) va fi disponibila, fiind deasupra stivei, si va putea fi scoasa prima (First Output).

Stiva este folosita implicit in mecanismul de apel al procedurilor.

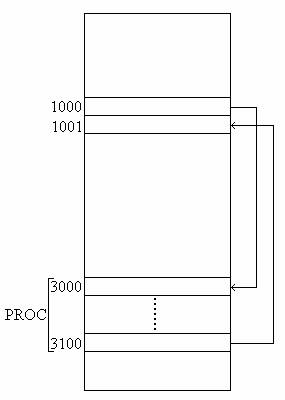

Fig. 2.

Figura 2 ilustreaza un astfel de caz. Atunci cand s-a ajuns cu pointerul de instructiuni (E)IP la adresa 1000, se executa un apel la procedura PROC care se gaseste in memorie la adresa 3000. Atunci cand se termina de executat procedura, trebuie sa ne intoarcem la prima instructiune de dupa instructiunea de apel procedura (1001 in cazul nostru). Deci, adresa 1001 trebuie sa fie memorata undeva pentru ca la revenirea din procedura sa reluam programul din acel loc.

Stiva se foloseste pentru a memora aceasta adresa de revenire. Microprocesorul este proiectat astfel incat, la executia unui apel de procedura (CALL), sa salveze automat in stiva adresa de memorie care contine instructiunea urmatoare din secventa (de fapt continutul registrului IP). Cand se intalneste in procedura instructiunea RETURN (revenire din procedura), tot automat microprocesorul ia din varful stivei adresa memorata anterior si o incarca in registrul (E)IP, executand apoi instructiunea gasita la aceasta adresa (adica instructiunea de la adresa 1001).

Putem defini stiva ca un concept abstract de structura de date, asupra carora opereaza instructiuni special proiectate in acest scop.

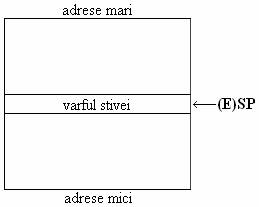

O zona de stiva este caracterizata de o adresa curenta, numita adresa varfului stivei, care la microprocesoarele Intel este adresata prin registrul (E)SP (stack pointer - indicator de stiva). Operatiile de baza cu stiva sunt PUSH (depune un cuvant in stiva) si respectiv POP (extrage un cuvant din stiva).

La microprocesoarele pe 16 biti, cuvintele transferate in stiva sunt de 16 biti (2 octeti), deci adresa curenta a varfului stivei se va incrementa sau decrementa cu 2 la fiecare operatie. Similar, la microprocesoarele pe 32 biti se poate lucra cu operanzi avand fie 16, fie 32 biti, in al doilea caz varful stivei fiind incrementat sau decrementat cu 4 la fiecare operatie. Figura 3 prezinta modul de actiune al unei operatii PUSH.

Fig. 3.

Se observa ca stiva 'creste' in jos pe masura ce se depun date in ea. La fel ca in cazul oricarui segment, marimea sa maxima este de 64 Ko la microprocesoarele pe 16 biti si 4 Go la cele pe 32 biti. Pot exista mai multe stive definite la un moment dat, dar numai una este activa.

Stiva este folosita explicit la salvari si refaceri de date, transmiterea parametrilor catre proceduri etc. Implicit se foloseste in cazul apelurilor de procedura. De asemenea, programele care permit definirea si folosirea functiilor recursive folosesc stiva pentru memorarea valorilor intermediare ale parametrilor si valorilor functiilor.

Procesoarele Intel din seria x86 fac parte din categoria procesoarelor numite CISC (Complex Instruction Set Computer - calculator cu set complex de instructiuni). Acestea sunt procesoare la care setul de instructiuni cuprinde un numar mare de operatii implementate. Totodata, acestea pot lucra cu mai multe tipuri de operanzi; pentru unele asemenea tipuri, adresa operanzilor este calculata intr-un timp relativ lung si abia dupa aceea se poate executa instructiunea propriu-zisa. S-a vazut incepand chiar de la calculatoarele mari (mainframe) ale anilor 1950 ca executia operatiilor simple cu operanzi in registri consuma mai putin timp de calcul. In plus, o data cu dezvoltarea software-ului de aplicatii si prin studii statistice efectuate de companii ca IBM s-a demonstrat ca instructiunile complexe din procesoarele CISC sunt rareori folosite, preferandu-se folosirea a catorva instructiuni simple in locul uneia mai complexe. Astfel, 10% din setul de instructiuni al unui procesor CISC sta la baza a peste 90% din totalul codului generat de un compilator ca PASCAL. Cercetarile s-au indreptat catre proiectarea unor procesoare cu instructiuni mai putine, cu multi registri si memorie imediata (cache) in care sa fie retinute datele temporare, toate acestea conducand la o viteza mai mare. Astfel au aparut procesoarele RISC (Reduced Instruction Set Computer - calculator cu set redus de instructiuni). Acestea s-au dezvoltat imediat ce tehnologia a permis obtinerea de memorie ieftina.

Simplitatea setului de instructiuni, modul de adresare mai simplu care necesita un singur acces la memoria principala intr-un singur impuls de ceas, precum si executia instructiunilor in structuri de tip pipeline au permis proiectarea unor unitati de executie superscalare, care permit executia mai multor instructiuni simultan. Aceasta au dus la succesul structurilor de tip RISC, care s-au impus alaturi de cele mai vechi de tip CISC. In ultimii 15 ani nu s-au mai proiectat noi structuri CISC.

Datorita simplitatii structurale, necesarul de siliciu este mai mic si astfel a aparut posibilitatea de integrare pe cip a unor memorii si unitati de executie multiple. Toate acestea au facut ca procesoarele RISC sa fie mai performante decat cele de tip CISC.

Procesoarele noi din seria x86 folosesc in structura lor tehnici RISC, pastrand insa vechea structura CISC. Acest set de instructiuni complex face ca software-ul mai vechi sa poata rula si pe procesoarele actuale.

Procesoare reprezentative de tip RISC sunt SPARC, MIP si ALPHA, care insa nu au reusit sa atinga succesul familiei x86.